Als de tijdstempel wordt gegenereerd door software, is de kloksynchronisatie in het bereik van enkele tienden microseconden tot milliseconden.

Indien echter uitgevoerd in hardware (FPGA), zal de nauwkeurigheid van de tijdstempel overeenkomen met de interne klok van de FPGA, die afhankelijk van de gebruikte frequentie, en in het bereik van 20-50 ns liggen. Hiermee is een synchronisatie tussen master en slave klokken in het bereik van tientallen nanoseconde mogelijk is .

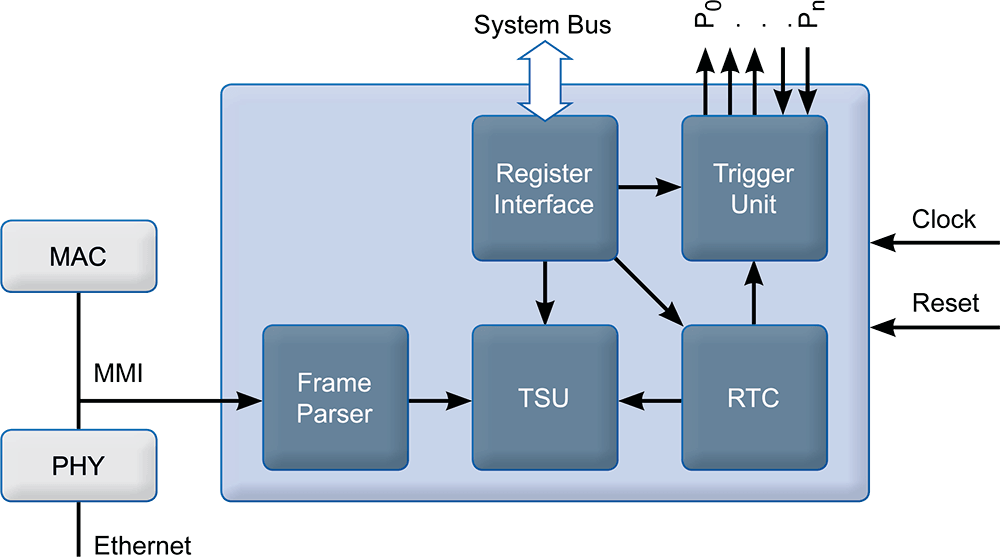

Met behulp van de trigger-eenheid (TRU), kunnen veranderingen van de digitale ingangssignalen worden vastgelegd met chronologische precisie via tijdstempels. Bovendien is het mogelijk digitale uitgangssignalen te genereren, waarvan de starttijd en de frequentie exact kan worden gespecificeerd.

De IEEE1588 IP Core is bedoeld voor:

- Gebruik in een FPGA met interne soft-CPU zoals de Altera NIOS, die de IEEE1588-protocol-software draait. IEEE1588 als één chip-oplossing;

- Gebruik in een FPGA gecombineerd met een externe processor die de IEEE1588-protocol software en applicatiesoftware draait.

In beide gevallen zijn er geen real-time eisen aan de software omgeving nodig. Het is voldoende om de IEEE1588-protocol-software cyclisch draaien, elke circa 10 tot 100 ms. Dit resulteert in een CPU belasting van minder dan 1%.

Kenmerken

- Real-time klok (RTC) instellen en aanpassen via software

- Tijd stempelen van externe input signalen via de trigger-eenheid

- Triggering van externe uitgang signalen op basis van configureerbare timers

- GMII-interface voor inkomende en uitgaande sync-bericht detectie (aanpassingen voor MII- en RMII-interfaces zijn bij de levering inbegrepen)

- Ondersteuning voor IEEE1588-versie 1 (IEEE1588-2002) en 2 (IEEE1588-2008)

- Tijdsaanduiding van IPv4, IPv6 en IEEE 802.3 (laag 2) berichten. Ondersteuning kan worden geactiveerd in zowel de FPGA-ontwerp als in de software.

- Standaard adres-/data-bus-interface

- Bufferopslag voor tijdstempels en aanvullende informatie voor het bericht toewijzing incl. de mogelijkheid om interrupts te generen

- Variabele externe klokfrequenties mogelijk

- Generatie van een externe PPS-signaal voor het meten van de kloknauwkeurigheid

| Technische gegevens | |

| Grootte | Circa 2000 logische elementen (Altera) |

| Nauwkeurigheid | ±150 ns (externe klok FPGA @ 50 MHz) ±75 ns (externe klok FPGA @ 80 MHz) |

| Beveiliging | Gecodeerde IP-Core voor Altera FPGA's |

| Leveromvang |

| - Altera Mega Core (volledige licentie of OpenCore+) |

| - Gecodeerde VHDL-code |

| - Device driver en demo applicatie in C |

| - Gebruikershandleiding |

| - Snelstart handleiding |

| - Technische ondersteuning (tijdgelimiteerd) |

Aanvullende diensten

De onderstaande diensten zijn géén onderdeel van de standaard leveromvang.

Onderhoudsovereenkomst

Als aanvulling op het softwarepakket, biedt we een onderhoudsovereenkomst dat de levering van de volgende diensten voor de duur van de overeenkomst bestaat uit:

- Gratis updates en het oplossen van problemen

- Technische ondersteuning

Ondersteuning bij de implementatie

Als extra dienstverlening, kunnen we ook de aanpassing, implementatie en het testen van de IEEE1588 IP Core binnen uw hardware of applicatie verzorgen.

IEEE 588 PTP protocol Software

De IEEE1588-protocol-software maakt een eenvoudige, snelle ontwikkeling van de IEEE 1588-compatibele apparaten mogelijk op basis van de IEEE1588 IP Core.