If the time stamp is generated by software, the clock synchronization is in the range from several 10 µs up to milliseconds.

If done in hardware (FPGA), the accuracy for the time stamp generation corresponds to the FPGA interal clock, which is depending on the frequency in the range of 20-50 ns. So a timer synchronization between master and slave clock in the double-digit nanosecond range is possible.

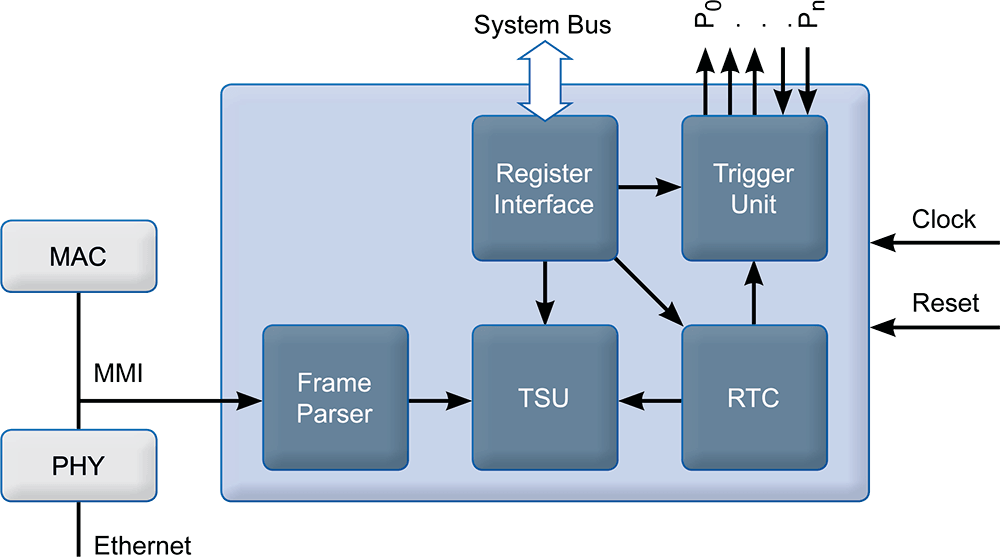

Using the trigger unit, changes of digital input signals can be captured chronological exactly via time stamps. In addition, it is possible to generate digital output signals, at this the starting time and the frequency can be specified exactly.

De IEEE1588 IP Core is intended for:

- Usage with a FPGA internal soft CPU like the Altera NIOS, running the IEEE1588 protocol software also. IEEE1588 device as an one chip solution;

- Usage with an external CPU running the IEEE1588 protocol software and application software.

In both cases no special real-time requirements to the software environment are needed. It is completely sufficient to run the IEEE1588 protocol software cyclically, approx. every 10 - 100 ms. This results in a CPU load of less than 1 %.

Features

- Real time clock setting and adjustment via software

- Time stamping of external input signals via the trigger unit

- Triggering of external output signals based on

configurable timers - GMII interface for incoming and outgoing sync message detection (converters for MII and RMII are included in the scope of delivery)

- Support for IEEE1588 version 1 (IEEE1588-2002) and 2 (IEEE1588-2008)

- Time stamping of IPv4, IPv6 and IEEE 802.3 (layer 2) messages. Support can be activated in both the FPGA design and in the software.

- Standard address/data bus interface

- Buffer storage for time stamps and additional information for the message assignment incl. the possibility of interrupt generation

- Variable external clock frequencies possible

- Generation of a external PPS signal for clock accuracy measurements

| Technical Data | |

| Size | Approx. 2000 logic elements (Altera) |

| Accuracy | ±150 ns (external clock FPGA @ 50 MHz) |

| ±75 ns (external clock FPGA @ 80 MHz) | |

| Security | Encrypted IP-Core for Altera FPGAs |

| Contents of delivery |

| - Altera Mega Core (full license or OpenCore+) |

| - Encrypted VHDL-code |

| - Device driver and demo applicatie in C |

| - User Manual |

| - Quick Reference Manual |

| - Technical support (time limited) |

Additional services

The services below are not included in the content of standard delivery.

Maintenance agreement

As a supplement to the software package, Ixxat offers a maintenance agreement that includes the provision of the following services for the term of the agreement:

- Free updates and troubleshooting

- Adaptation to the latest standard

- Technical support

Implementation support

As an additional program offering, we can also handle the adaptation, implementation and testing of the IEEE1588 IP Core on your system.

IEEE 1588 PTP Protocol Software

The IEEE 1588 protocol software enables simple, rapid development of IEEE 1588 compliant devices based on the IEEE1588 IP Core.